LAPORAN AKHIR 1 M4

2. Alat dan Bahan [Kembali]

Alat

a. Jumper

Gambar 1. Jumper

Bahan

a. IC 74LS112 (J-K Flip-Flop)

b. CD4013B (D Flip-Flop)

c. Gerbang AND (IC 7048)

d. Gerbang OR (IC 7432)

e. Power DC

3. Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian [Kembali]

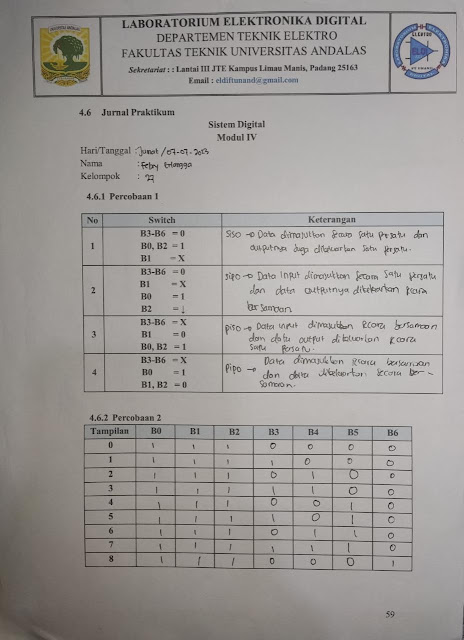

Pada percobaan 1 pada modul 4 ini, kami merangkai rangkaian berdasarkan percobaan pada modul, terdapat 4 kali percobaan, sehingga diperoleh:

- Pada percobaan pertama didapatkan outputnya itu berupa shift register jenis Serial In Serial Out (SISO). Dimana pada saat B1 kita hidupkan atau kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara satu persatu dari shift register.

- Pada percobaan kedua, pada saat B1 kita hubungkan dengan vcc maka data akan masuk secara satu persatu ke dalam shift register, selanjutnya pada saat B2 kita beri trigger falltime kondisi ini bertujuan untuk mengambil data yang ingin kita masukkan, dan pada saat B1 kita hubungkan ke ground maka data akan keluar secara serentak dari shift register. Maka dari itu keadaan ini disebut Serial In Paralel Out (SIPO).

- Pada percobaan ketiga, B3 sampai B6 merupakan inputan dari datanya. Setelah kita mengatur dari inputannya, maka inputannya akan masuk secara serentak ke dalam shift register tersebut dan ketika data tersebut sudah masuk, maka data akan keluar dari shift register secara satu persatu. Maka dari itu kondisi ini disebut shift register jenis Paralel In Serial Out (PISO).

- Pada percobaan keempat, B3 sampai B6 merupakan inputan untuk kita mengatur datanya. Pada saat rangkaian dijalankan, data akan langsung masuk ke dalam shift register secara serentak dan akan keluar secara serentak juga dari shift register. Maka dari itu shift register disebut jenis Paralel In Paralel Out (PIPO).

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

1) Analisa output yang dihasilkan oleh tiap-tiap kondisi

- Pada percobaan pertama output yang dihasilkan secara satu persatu karena merupakan serial out

- Pada percobaan kedua, output yang dihasilkan keluar secara bersamaan karena merupakan paralel out

- Pada percobaan ketiga, output yang dihasilkan keluar secara satu persatu karena merupakan serial in

- Pada percobaan keempat, output yang dihasilkan keluar secara bersamaan karena merupakan serial out

2) Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip-flop. Bandingkan output yang dihasilkan

Jawab :

Jika ditinjau dari output yang dihasilkan,maka tidak akan ada variasi yang dihasilkan. Yang nantinya akan diperoleh rangkaian yang menggunakan prinsip SISO,SIPO,PISO ,PIPO. Karena fungsi gerbang AND disini adalah sebagai pengontrol data

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar